# **Searching for the Milli-Volt Switch**

## Eli Yablonovitch,

# Winton Inaugural Symposium on Energy Efficiency **Cambridge**, United Kingdom **Oct. 1, 2012**

A Science & Technoloav Center

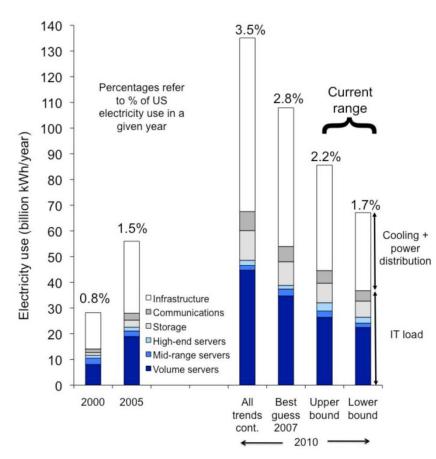

# Data Center Electricity Usage

In 2010, data centers accounted for ~1.3% of all electricity use worldwide, ~2% of all electricity use in the U.S.

Google's new data center in Hamina, Finland, has an energy-efficient cooling system that uses seawater from a nearby bay.

J. Koomey, Growth in Data center electricity use 2005 to 2010 (Analytics Press, Oakland, CA), 201<sup>2</sup>

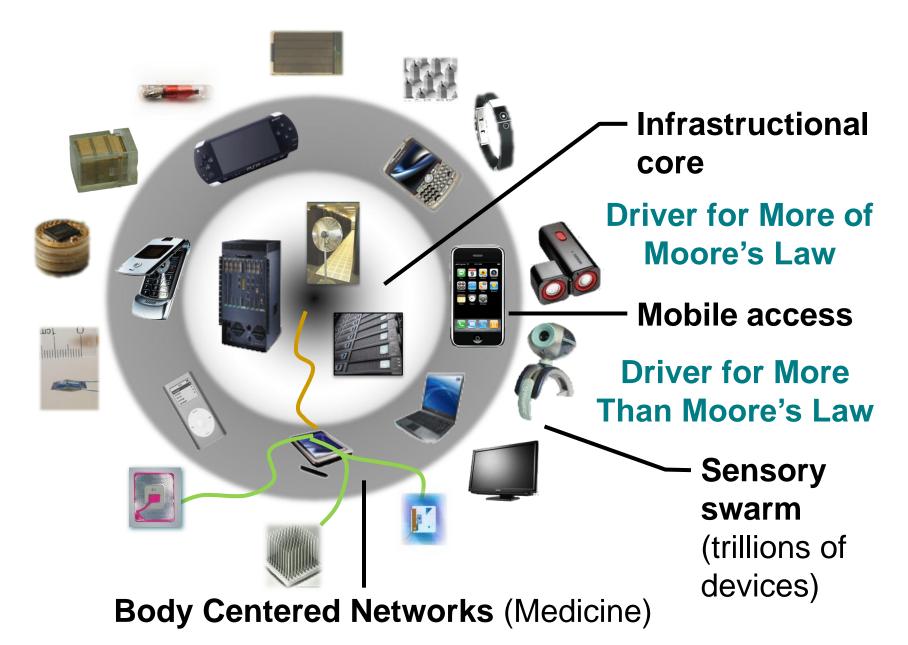

## Vision for 2020: Swarms of Electronics:

# Power Usage Rising Faster Than Past Trend

Because power consumption ∞V<sub>dd</sub><sup>2</sup> and V<sub>dd</sub> (operation voltage) scaling has slowed after 0.13µm node.

| Technolog       | 0.25  | 0.18  | 0.13  | 90    | 65    | 45    | 32    | 22    | 16    |

|-----------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| y Node          | μm    | μm    | μm    | nm    | nm    | nm    | nm    | nm    | nm    |

| V <sub>dd</sub> | 2.5 V | 1.8 V | 1.3 V | 1.2 V | 1.1 V | 1.0 V | 0.9 V | 0.8 V | 0.7 V |

High Performance ITRS Roadmap

# What is the energy cost of reading out your flash memory?

Read the current going through a resistor, in the presence of noise:

$$(\Delta i)^2 = 2q \ i \times \Delta f$$

.....Shot Noise

$(\Delta i)^2 = \frac{4kT}{R} \times \Delta f$ ....Johnson Noise

Required voltage V = iR >>  $2kT/q \sim 50mVolts$

Signal – to – Noise Ratio =

$$\frac{i}{\sqrt{2q} i\Delta f} = \sqrt{\frac{i}{2q} \Delta f}$$

$i > 2q \times \Delta f$

Required power iV > 2q  $\Delta f \times \frac{2kT}{q} = 4kT \times \Delta f$

With a safety margin: Energy Consumed ~ 40 kT per bit processed

## Units:

# ~40kT/bit of information

0.16 atto-Joules/bit of information

0.16 nano-Watts/Gbit/second

This is about 10<sup>6</sup> times less energy than we are using today!

What will be the energy cost, per bit processed?

- Logic energy cost ~40kT per bit processed

Storage energy cost ~40kT per bit processed

- 3. Communications currently >100,000kT per bit processed

There are many type of memory possible:

- 1. Flash

- 2. SRAM

- 3. Dram

- 4. Magnetic Spin

- 5. Nano-Electro-Chemical Cells

- 6. Nano-Electro-Mechanical NEMS

- 7. Memristor

- 8. Chalcogenide glass (phase change)

- 9. Carbon Nanotubes

## •

#### •

Similarly there are many ways to do logic.

But there are not many ways to communicate:

- 1. Microwaves (electrical)

- 2. Optical

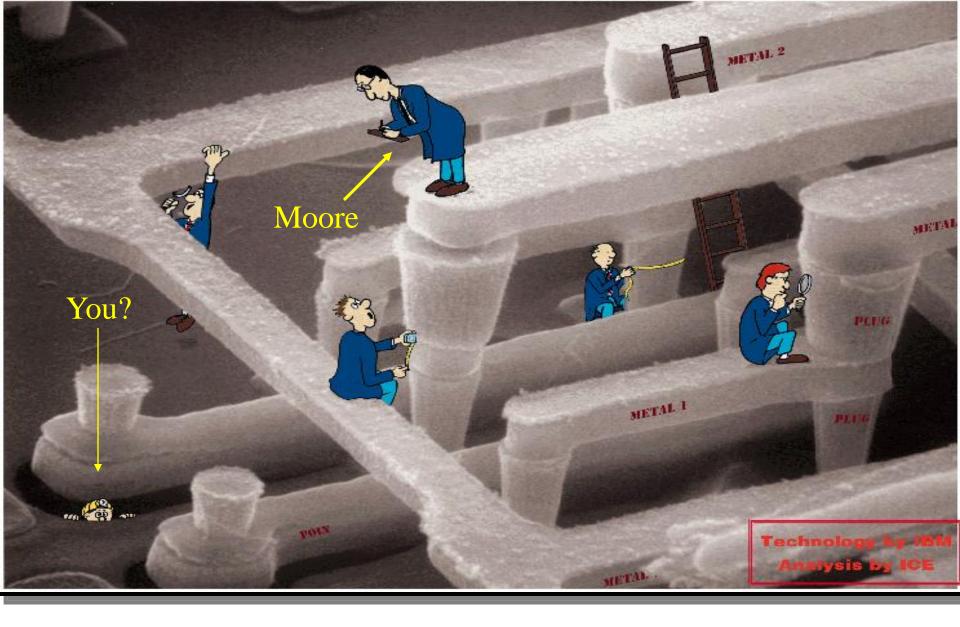

#### IBM's Power PC750 Microprocessor

Mag. 63,25

What is the energy cost for electrical communication?

$$\frac{V_{noise}^2}{\frac{V_{noise}^2}{R}} = 4kT R \Delta f$$

$$\frac{\text{Signal}}{\text{Energy}} \geq \frac{\text{Noise Power}}{\text{per bit}} = 4kT \text{ per bit}$$

All information processing costs ~ 40kT per bit. (for good Signal-to-Noise Ratio)

Great!

So what's the problem?

The natural voltage range for wired communication is rather low:

$V_{noise}^2 = 4kTR\Delta f$  $V_{noise}^2 = 4kTR\frac{1}{RC}$  $V_{noise}^2 = 4kT \times \frac{1}{C}$  $V_{noise}^2 = \frac{4kT}{q} \times \frac{q}{C}$  $V_{\text{noise}} = \sqrt{\frac{4kT/q}{100 \text{ mVolts}}} \times \frac{q/C}{10 \text{ uVolts}}$  $V \approx 1 \text{ mVolt}$

The wire wants 1000 electrons at 1mVolt each.

(to fulfill the signal-to-noise requirement >1eV of energy)

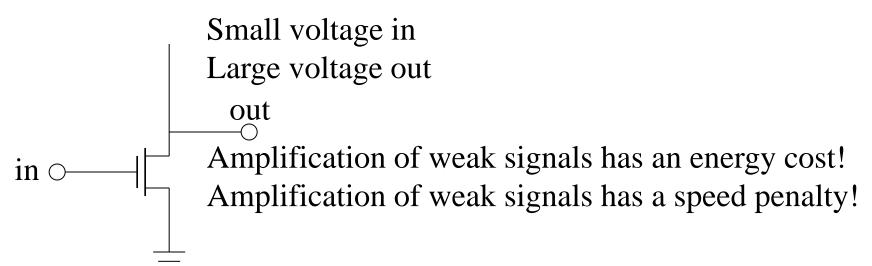

The natural voltage range for a thermally activated switch like transistors is >>kT/q, eg. ~ 40kT/q or about ~1Volt

Voltage Matching Crisis at the nano-scale!

If you ignore it the penalty will be  $(1Volt/1mVolt)^2 = 10^6$

The thermally activated device wants at least one electron at ~1Volt.

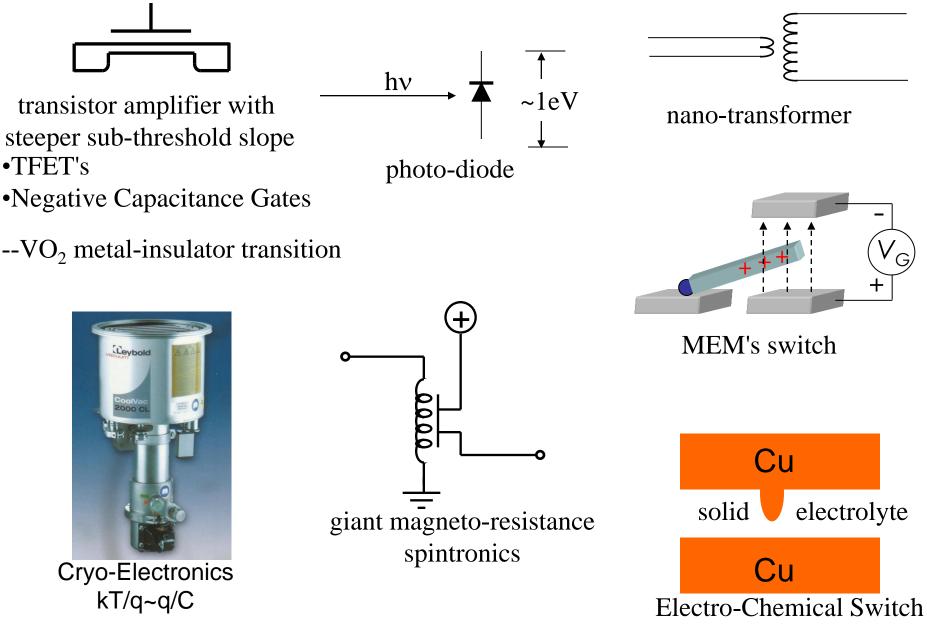

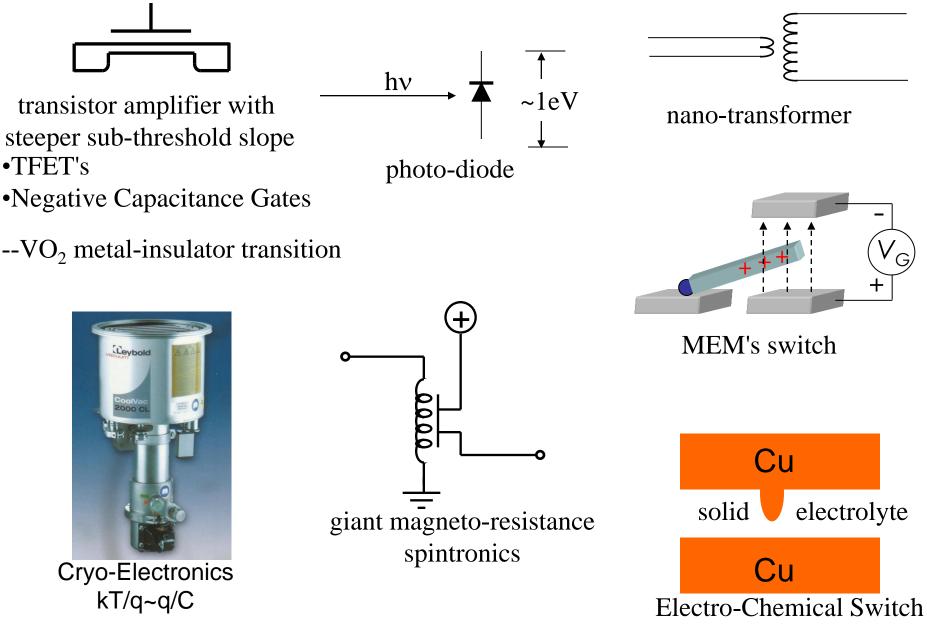

The New Switch has to Satisfy Three Specifications:

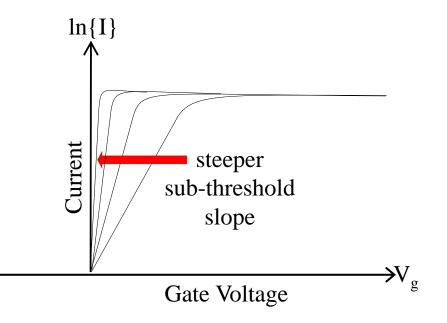

1. Steepness (or sensitivity) switches with only a few milli-volts  $60mV/decade \Rightarrow 1mV/decade$

2. On/Off ratio.  $10^6: 1$

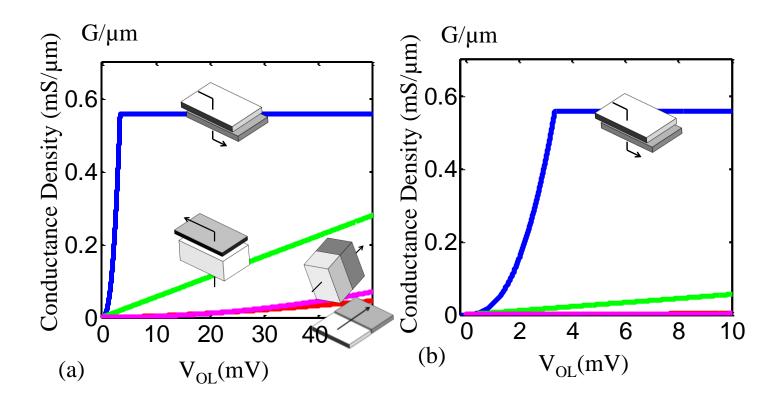

3. Current Density or Conductance Density (for miniaturization)

old spec at 1Volt: 1 mAmp/micron

our spec: 1 milli-mho/micron A low-voltage technology, or an impedance matching device, needs to be invented/discovered at the Nano-scale:

An amplifying transistor as a voltage matching device:

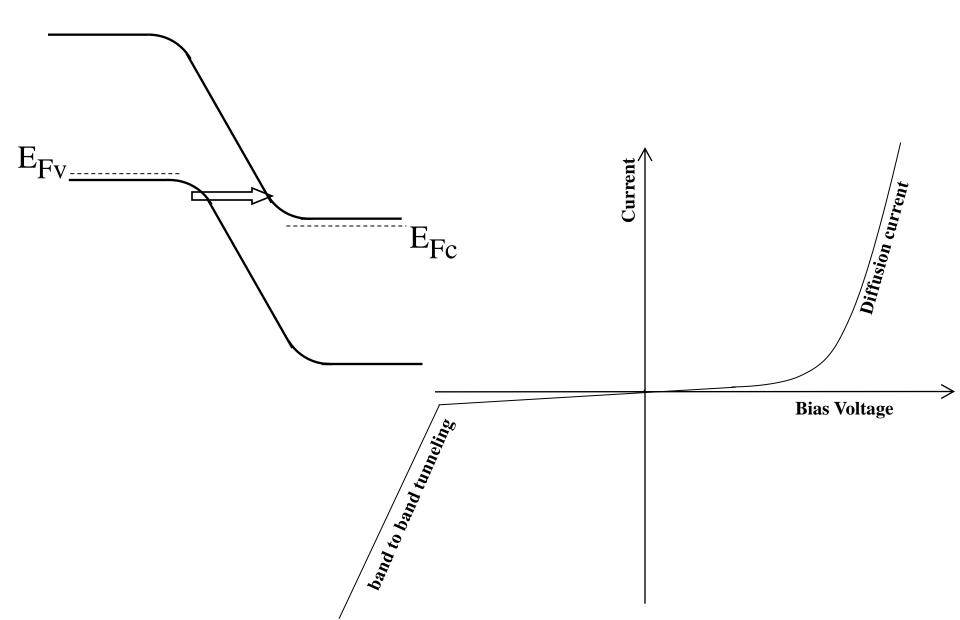

## The Zener Diode:

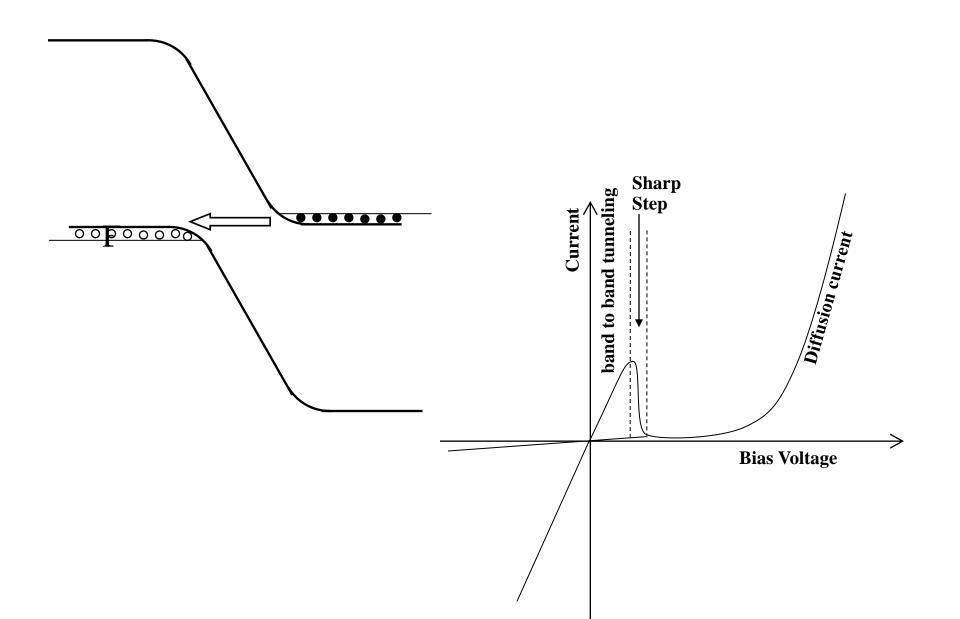

## The Esaki Diode:

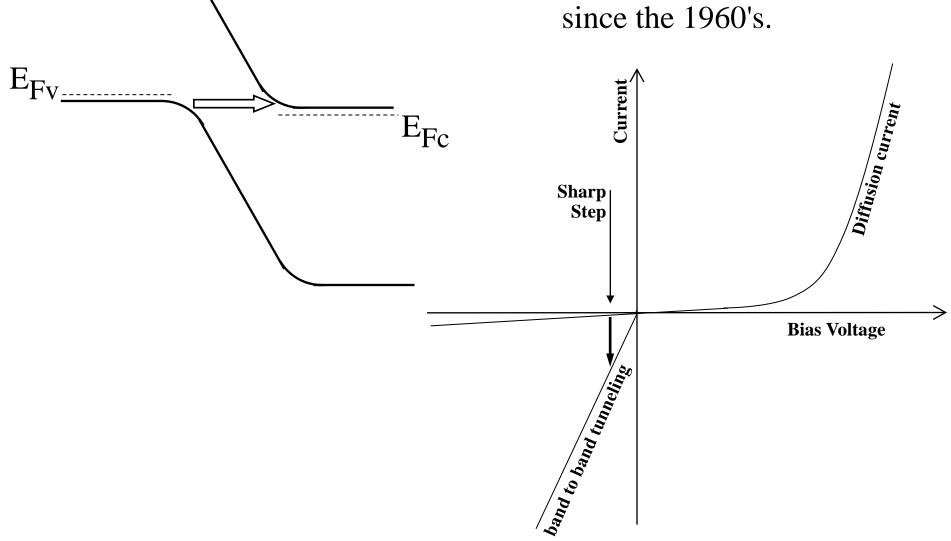

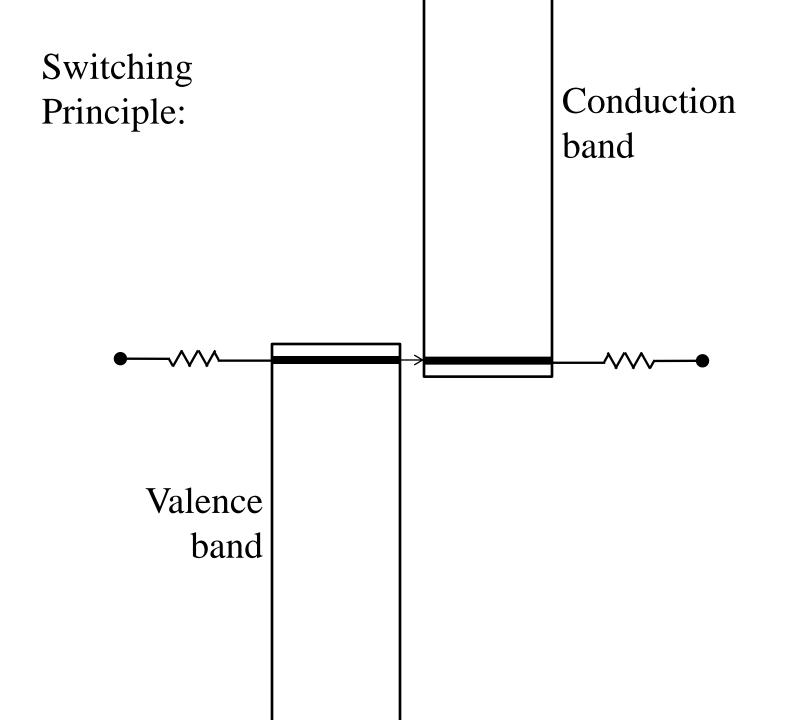

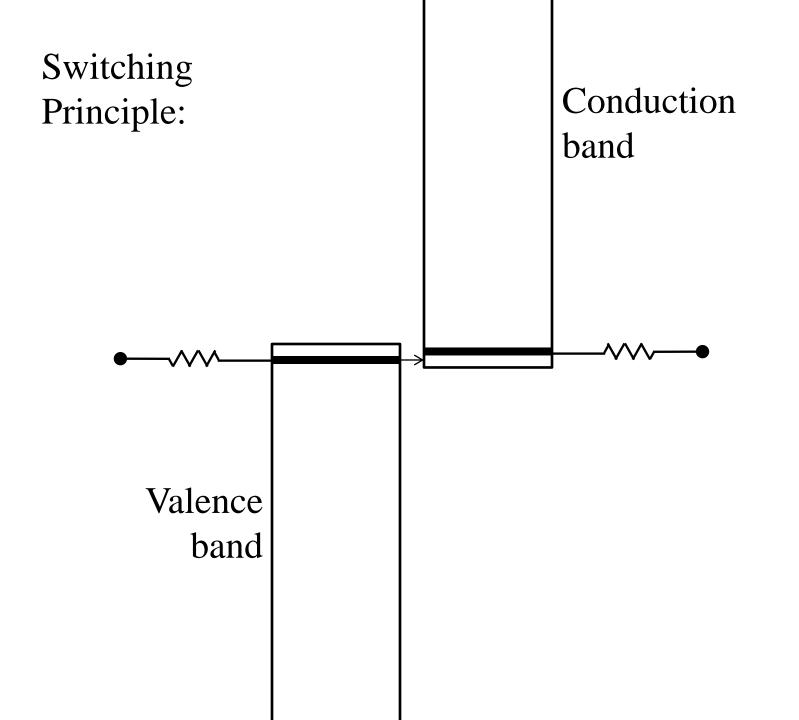

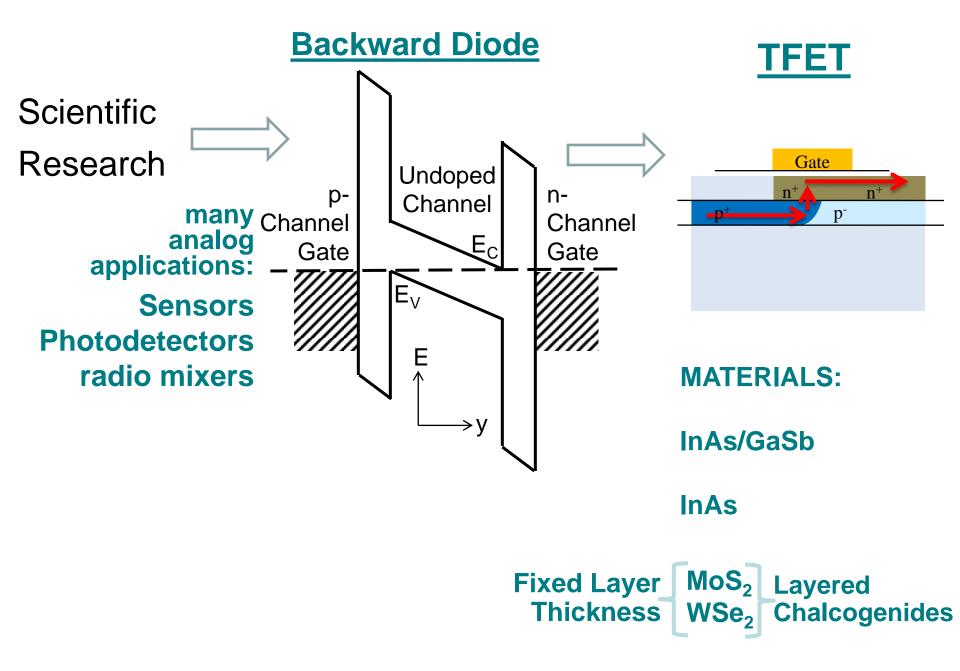

The Backward Diode as a Switch:

<u>The Backward Diode:</u> These have been routinely made in Ge homo-junctions, since the 1960's.

The Backward Diode as a Switch:

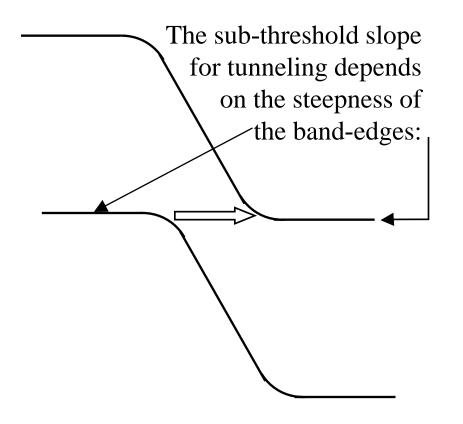

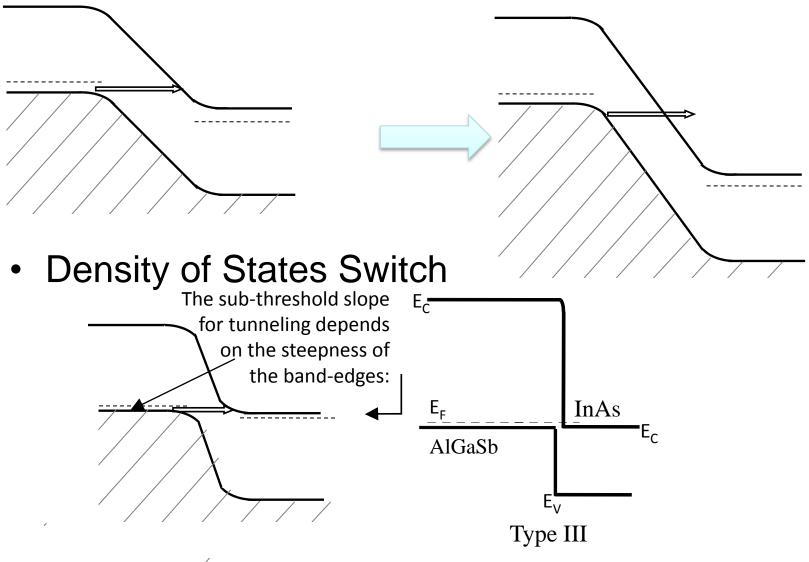

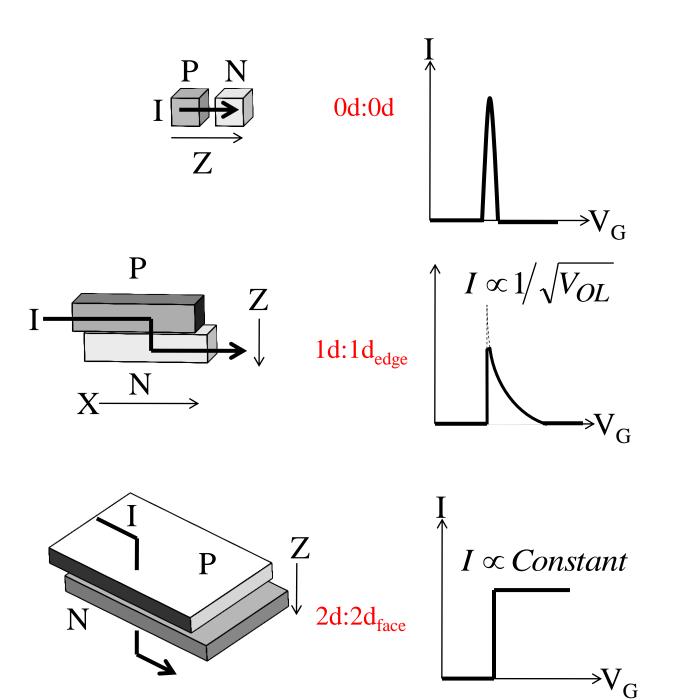

# 2 Ways to Obtain Steepness:

• Modulate the Tunneling Barrier:

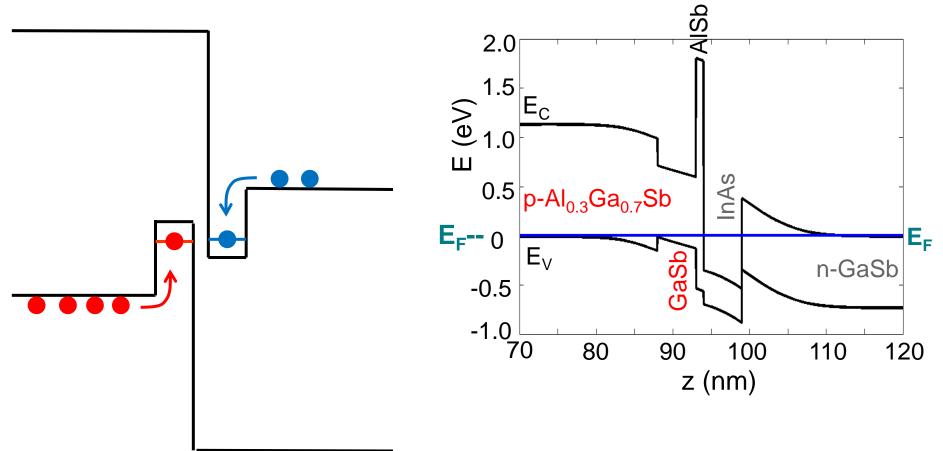

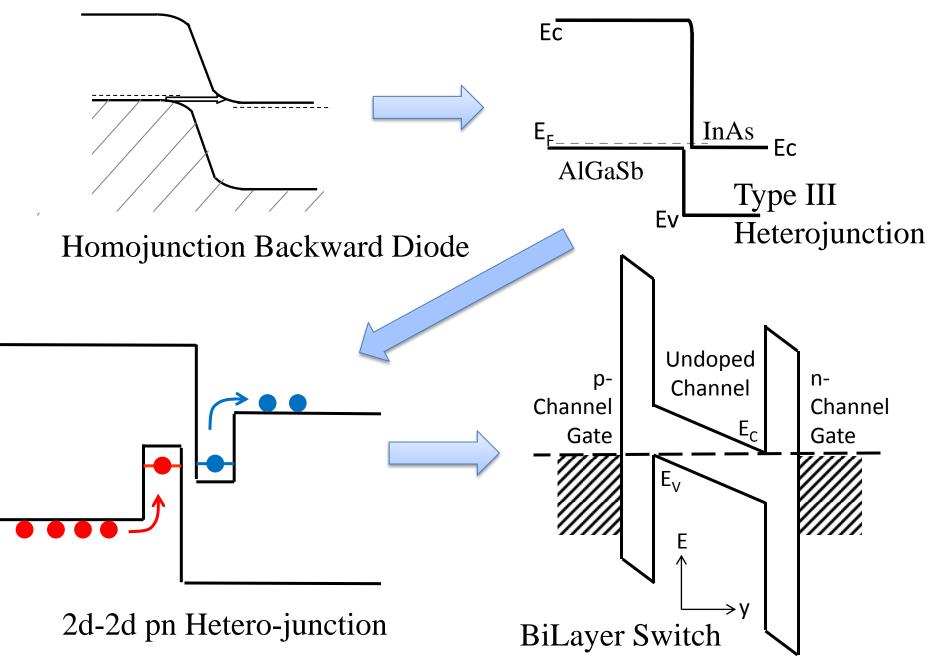

## **Type III band alignment**

### **Idealized structure**

$$\gamma$$

=2.34 meV

E<sub>Z</sub>=50 meV

$$T_{\text{device}} = 2.16\%$$

$L_{\text{X}} = 32 \text{ nm}$

$L_{\text{Z}} = 8.672 \text{ nm}$

m\*=0.1

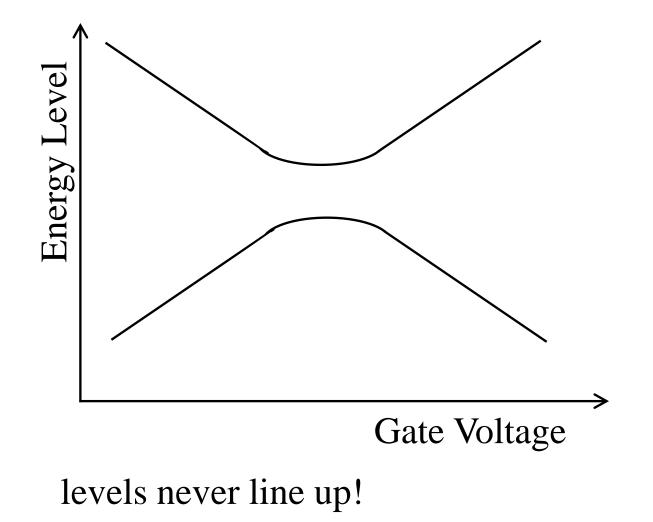

What could go wrong?

1. quantum-mechanical level repulsion:

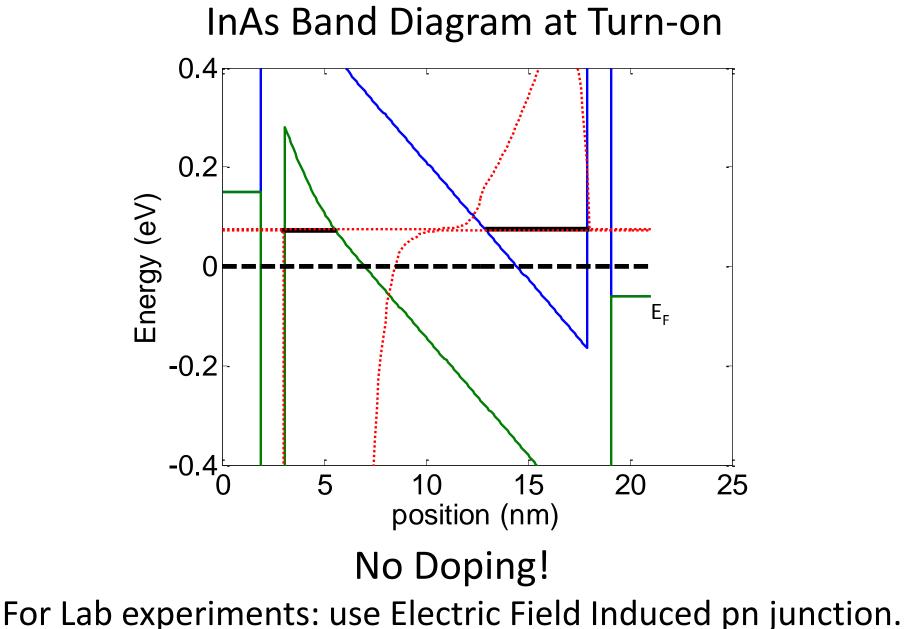

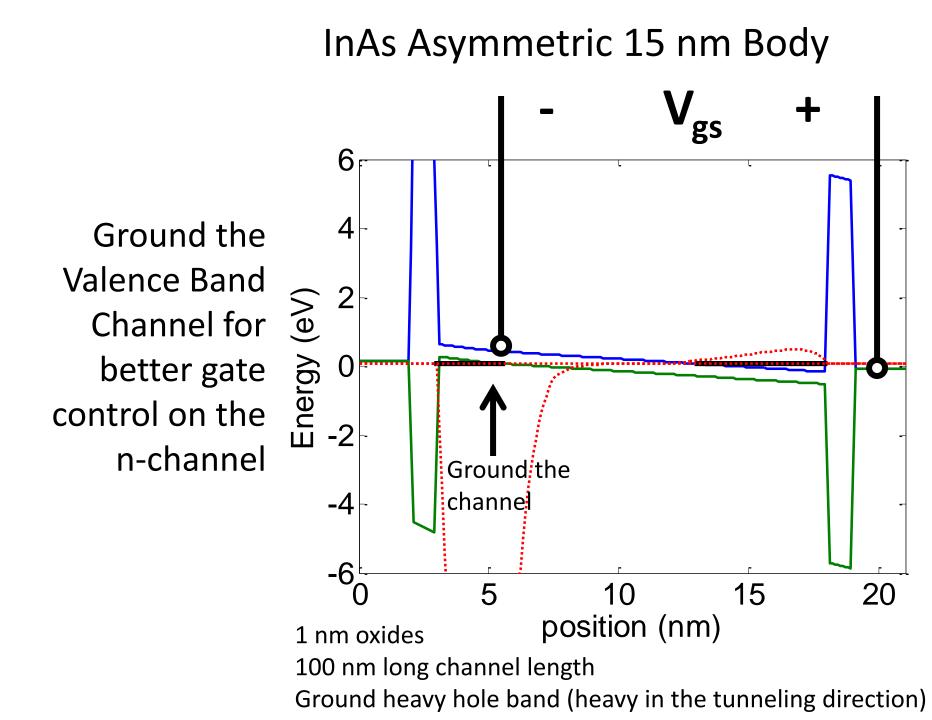

## **Evolution of the Tunnel Switch 2010-2012:**

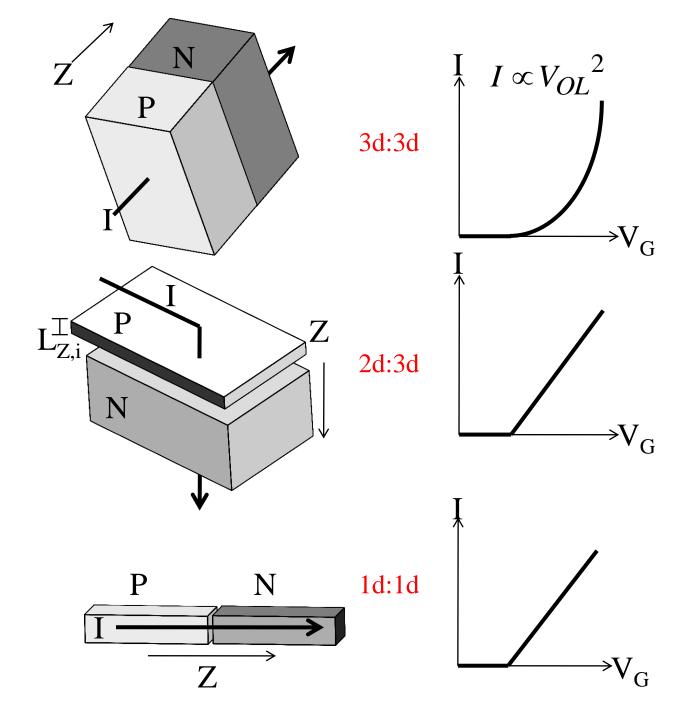

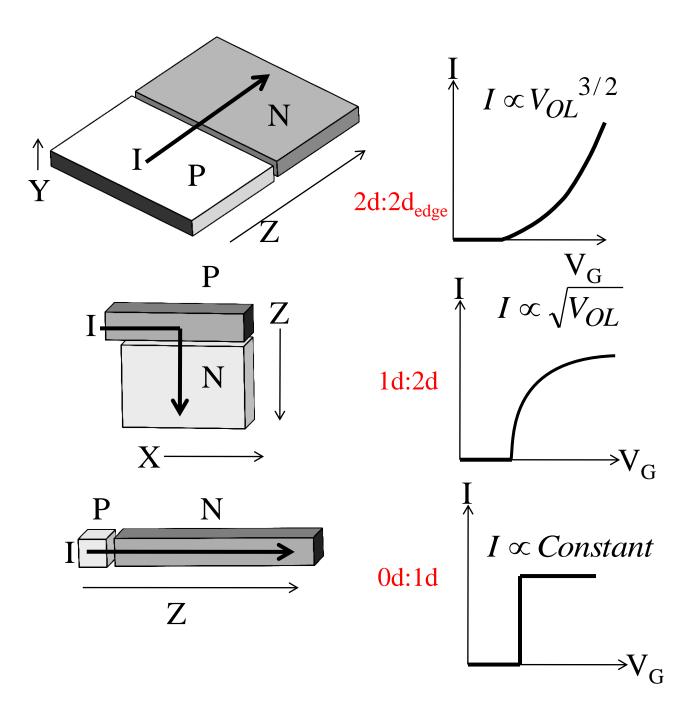

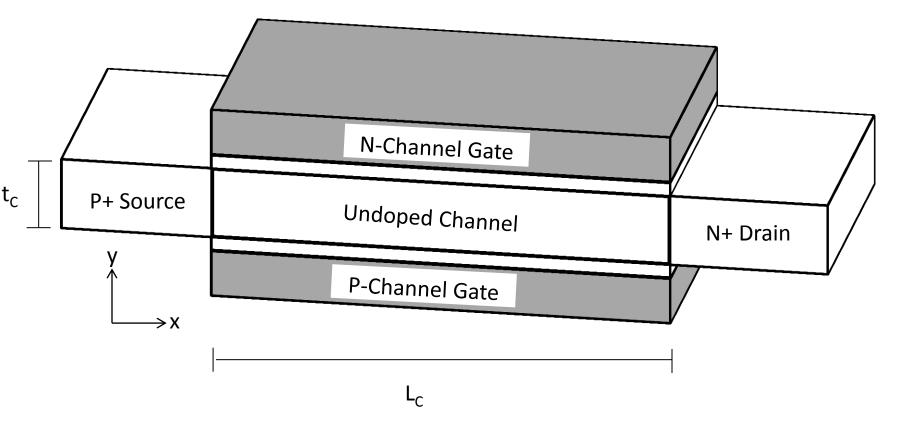

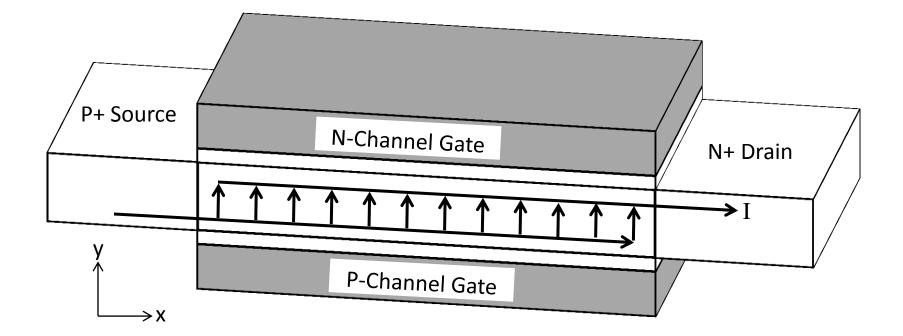

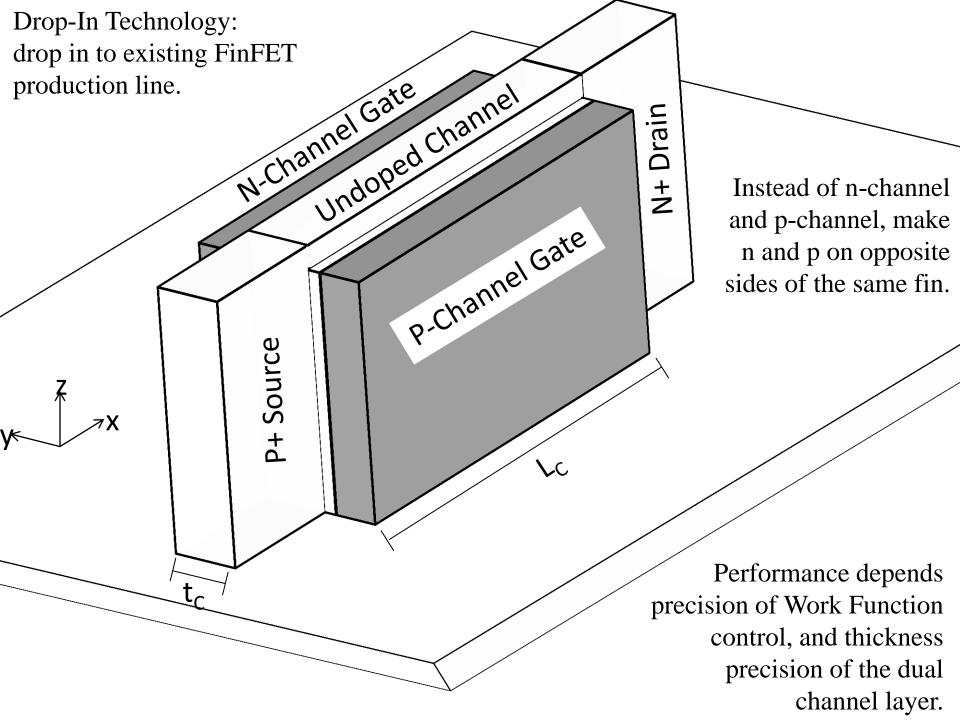

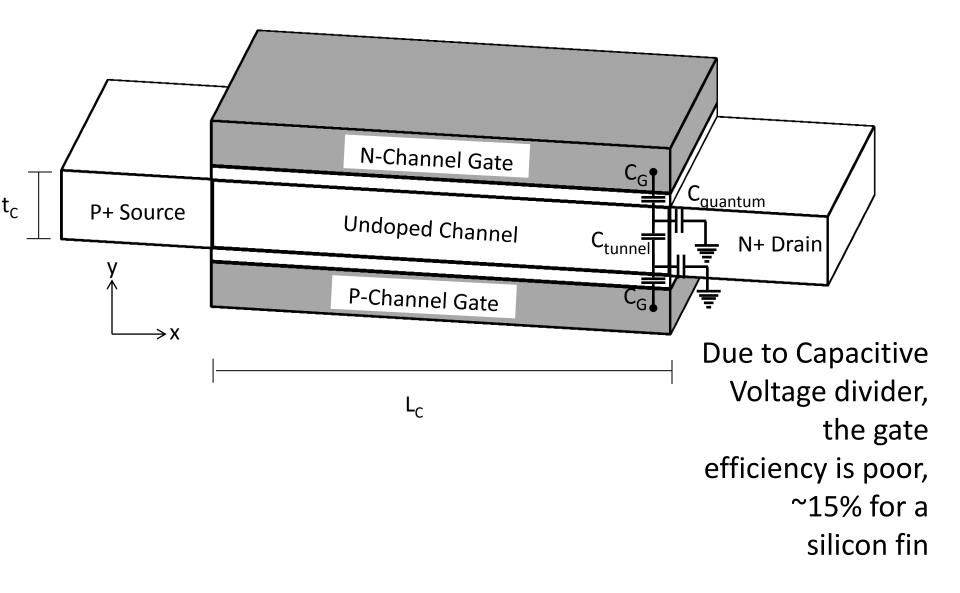

## The Bi-Layer pn-junction or the Bi-Layer Tunneling Field Effect Transistor

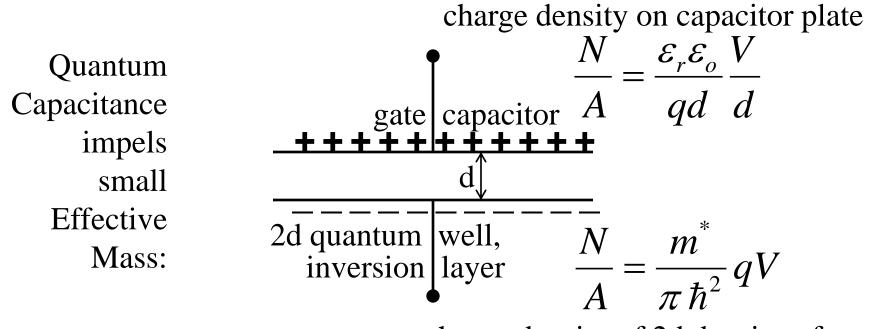

charge density of 2d density-of-states

Respectable gate efficiency requires:

$$\frac{qm^*}{\pi\hbar^2} < \frac{\varepsilon_r \varepsilon_o}{qd^2}$$

Respectable gate efficiency requires  $m^* < 0.1 m_o$

Try InAs, effective mass is lower, density of states is lower, and C<sub>quantum</sub> is lower.

The lower n-channel carrier density makes it easier to swing the energy level

Lower effective mass—easier tunneling

We need  $m_{eff} < 0.1$

For production use: Work Function induce pn junction.

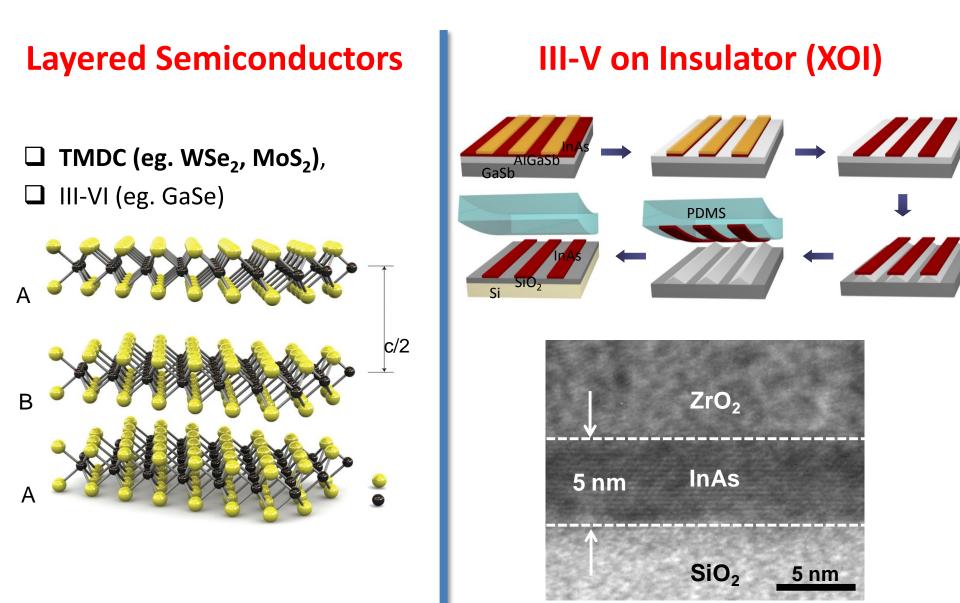

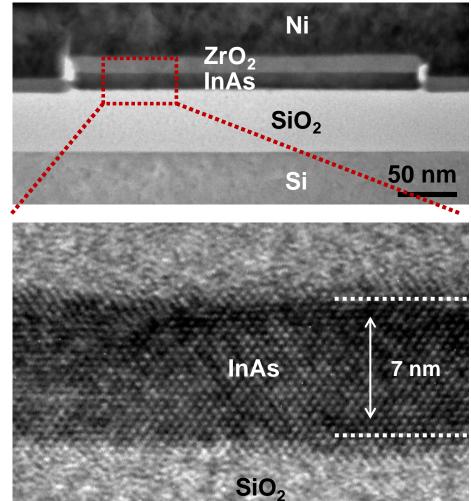

# 2D Nanomembranes for Novel Tunneling (A. Javey)

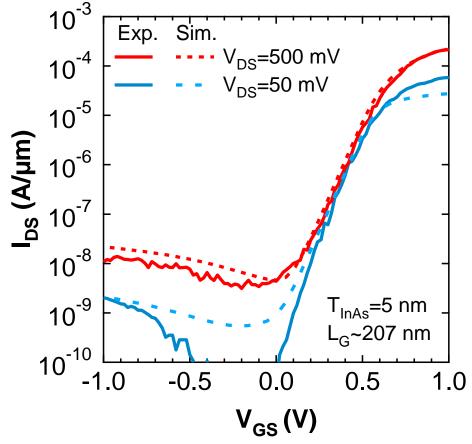

# High Performance InAs XOI n-MOSFETs

Electron Mobility: 1000-7000 cm<sup>2</sup>/Vs SS ~ 75 mV/decade  $R_c$ ~80  $\Omega\mu m$

Kuni Takei, et al, Nano Letters, 2011. Kuni Takei, et al, APL, 2011 H Ko, et al, Nature, 2010

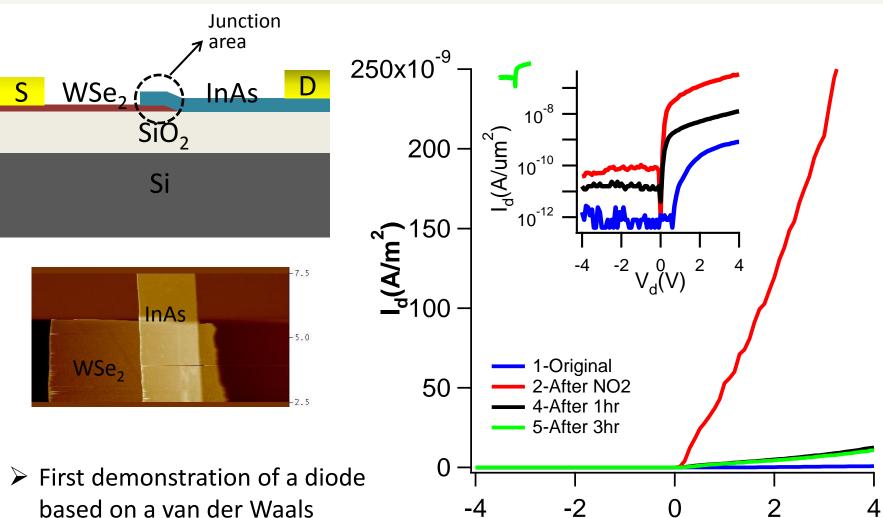

# InAs/WSe<sub>2</sub> Heterostructure

- based on a van der Waals heterojunctions.

- Clear rectifying behavior is observed

Steven Chuang, et al, submitted, 2012

$V_{d}(V)$

# Materials Approach:

Van der Waals 2D membranes:

- Removes lattice mismatch constraints

- Mix and Match: A wide range of heterojunctions is available

- □Atomically abrupt interfaces

# Roadmap:

## What keeps me up at night:

Band edges are simply not sharper than ~kT/3q, allowing us to pick up only a factor ~3 improvement.

#### What doesn't worry me:

Manufacturability and Yield. If we can demonstrate individual high-performing devices, then a large international effort will become directed toward these problems. A low-voltage technology, or an impedance matching device, needs to be invented/discovered at the Nano-scale: